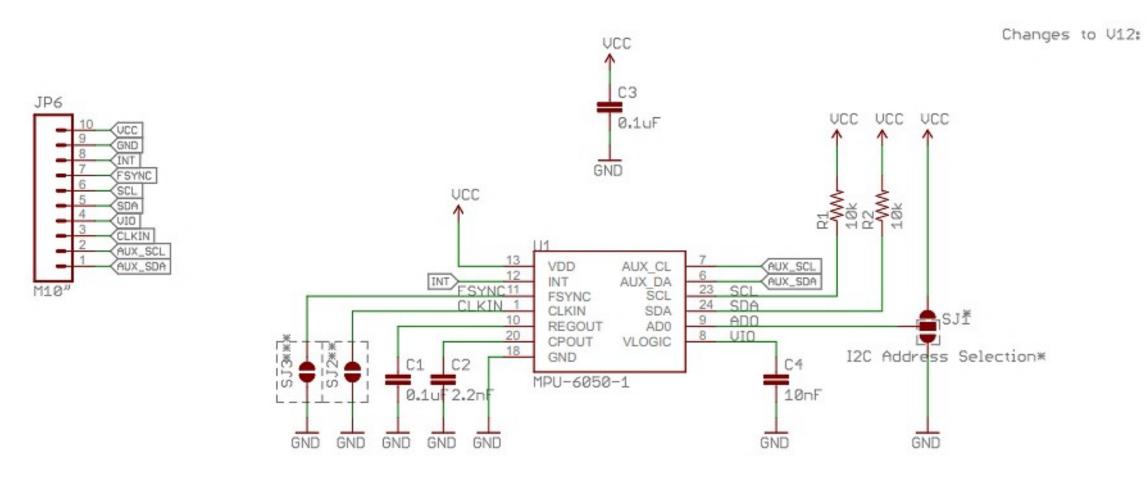

Changes to V11

SCL and SDA were switched on V10, fixed on V11

Broke out VLOGIC line

C2 was mislabled as 10nF, should have been 2.2nF.

Added selectable jumpers to CLK, FSYNC and AD0

Minor layout changes

Played around with IC footprint.

Added 4 small tcream squares to middle pad.

Rounded and elongated pads.

BOM changes YES C2 is now 2.2nF instead of 10nF

New Stencil YES

\* Two MPU-60X0s can be connected to the same I2C bus

The LSB bit of the 7 bit address is determined by the logic level on pin ADO.

Default Address = 0x68 (pin ADO is logic low)

Alternative Address = 0x69 (pin ADO is logic high)

\*\* Optional external reference clock input. Connected to GND by default.

Cut trace for external clock

open herdwere

**\*\***

Attribution Share-Alike 3.0 License

http://creativecommons.org/licenses/by-sa/3.0 🛇 🛇 O O

TITLE: Triple\_Axis\_Accelerometer-Gyro\_Breakd

Design by: J. Bartlett Revision By:E. Orosel

Released under the Creative Commons

REV: v12

Date: 7/23/2013 2:47:34 PM Sheet: 1/1

\*\*\* Frame synchronization digital input. Connected to GND by default

Cut trace for external sync